## 5UPER **INSTITUTE** FOR **SUSTAINED PERFORMANCE**,

ENERGY, AND RESILIENCE

Abstract: SUPER's Energy thrust is charged with understanding to design software- and hardware-aware optimization techniques that enable computations within a power bounds and reduce the DOE's HPC energy footprint. Two focus areas have emerged within this thrust: software solutions that provide fine-grained access to the power measurements and energy efficiency research that utilizes these measurements to develop green optimization strategies. We highlight recent accomplishments in each area and present empirical results that illustrate SUPER's contributions in minimizing DOE's HPC energy requirements.

| Direct Power Reading: "micpower"                                                                                                                                                                                                                                                                                                                                                                                                                                                | Offloaded Power Reading: "host_micpower"                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>The "micpower" component runs in native mode – the actual application and PAPI are running natively on the co-process operating system – without being offloaded from a host system.</li> <li>Provides access to an on-board power sensor on the Xee which allows measurement of current and voltage (and power) for various Phi subsystems at ~50 ms resolution.</li> <li>Power values are periodically read from the contents of /sys/class/micras/power.</li> </ul> | <ul> <li>The "host_micpower" component appears more as PAPI is offloaded from the host system, and or running on Xeon Phi.</li> <li>Easier to measure power consumption of appethe Phi at fairly high resolution without actual MIC code directly.</li> <li>Power data exported through the MicAccess/ Intel MPSS).</li> </ul> |                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Events                                                                                                                                                                                                                                                                                                                         | Description                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | tot0,tot1                                                                                                                                                                                                                                                                                                                      | Total (average) power consumption over two different time windows                                                                                                                |

| The following Table provides a list of events that a user                                                                                                                                                                                                                                                                                                                                                                                                                       | pcie                                                                                                                                                                                                                                                                                                                           | Power measured at the PCI-express input (connecting CPU with the P                                                                                                               |

| can choose from to obtain power readings for an application running on the Xeon Phil co-processor:                                                                                                                                                                                                                                                                                                                                                                              | inst<br>imax                                                                                                                                                                                                                                                                                                                   | Instantaneous power consumption reading (uW)<br>Maximum instantaneous power consumption observed (uW)                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | c2x3,c2x4                                                                                                                                                                                                                                                                                                                      | Power measured at the input of the two power connectors located o                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | vccp<br>vddg<br>vddq                                                                                                                                                                                                                                                                                                           | Power supply to the cores (core rail)<br>Power supply to everything but the cores and memory (uncore rail)<br>Power supply to memory subsystem (memory rail) (current (uA), Volt |

For current and future systems power/energy are an important factor. On some current systems we can change the power draw of the different components in order to compute within a power budget or save energy. The next steps in this research is to extend the power/energy investigation from the cores towards the memory sub-system.

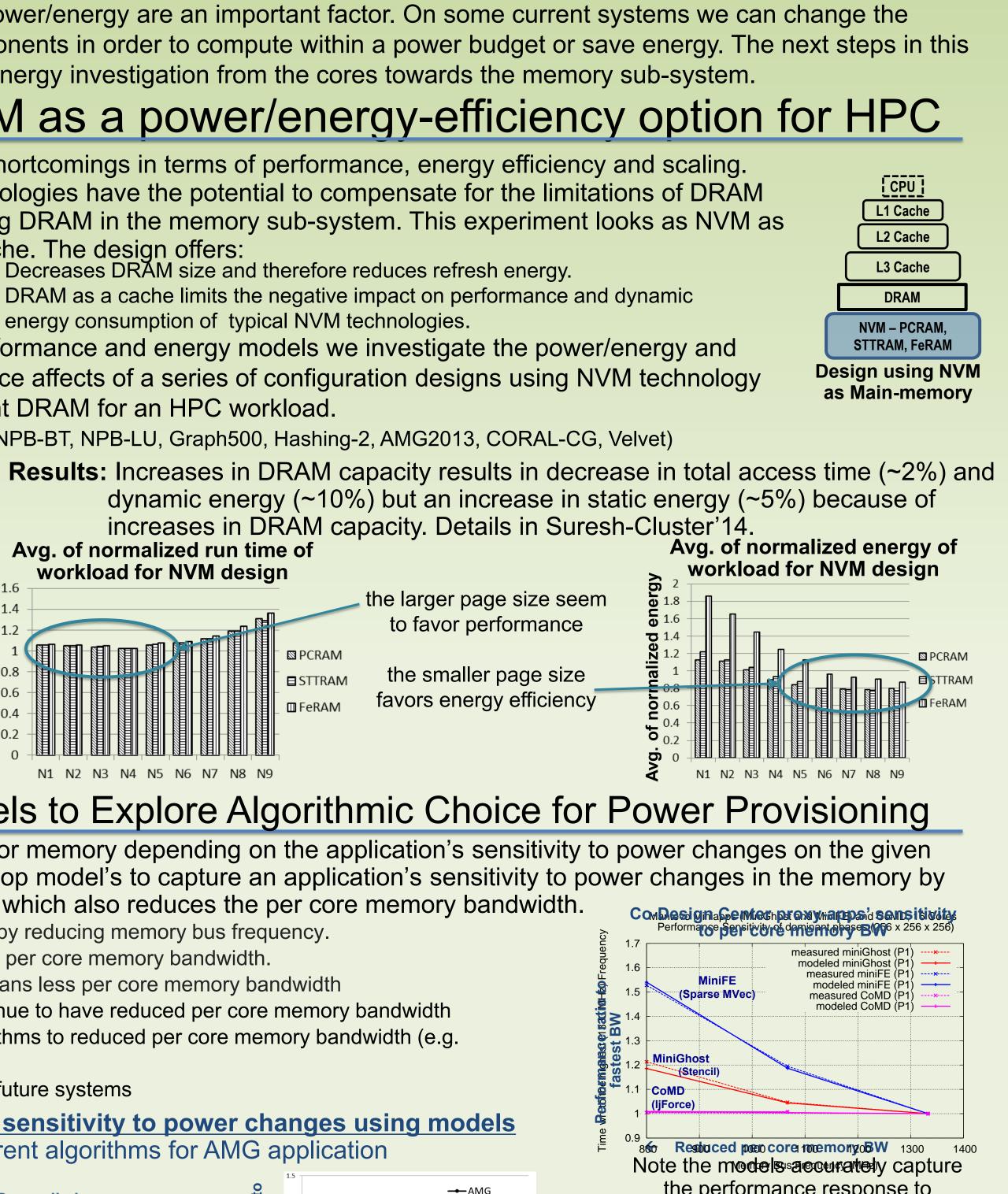

#### Investigating NVM as a power/energy-efficiency option for HPC

DRAM technology has several shortcomings in terms of performance, energy efficiency and scaling. Several emerging memory technologies have the potential to compensate for the limitations of DRAM when replacing or complementing DRAM in the memory sub-system. This experiment looks as NVM as main-memory with DRAM as cache. The design offers: • Decreases DRAM size and therefore reduces refresh energy.

• DRAM as a cache limits the negative impact on performance and dynamic energy consumption of typical NVM technologies.

**Experiment:** Using performance and energy models we investigate the power/energy and performance affects of a series of configuration designs using NVM technology to augment DRAM for an HPC workload.

(Workload: NPB-BT, NPB-LU, Graph500, Hashing-2, AMG2013, CORAL-CG, Velvet)

| Design Configurations |                                                           | tions         | <b>Nesults.</b> Increases in DrAw capacity results in decrease in |                                                                                                   |       |  |  |

|-----------------------|-----------------------------------------------------------|---------------|-------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|-------|--|--|

| Investigated          |                                                           |               |                                                                   | dynamic energy (~10%) but an increase in static                                                   |       |  |  |

|                       | Design                                                    | DRAM-         | Page-                                                             | increases in DRAM capacity. Details in Suresh-0                                                   | Clu   |  |  |

|                       | Name                                                      | capacity (MB) | size (KB)                                                         | Avg. of normalized run time of                                                                    |       |  |  |

|                       | <b>N1</b>                                                 | 128           | 4                                                                 | ق workload for NVM design                                                                         | >     |  |  |

|                       | N2                                                        | 256           | 4                                                                 | the larger page size seem                                                                         | lergy |  |  |

|                       | N3                                                        | 512           | 4                                                                 | to favor performance                                                                              | len   |  |  |

|                       | N4                                                        | 512           | 2                                                                 |                                                                                                   | zec   |  |  |

|                       | N5                                                        | 512           | 1                                                                 | <sup>1</sup> 0.8<br>0.6 0.6 □ STTRAM the smaller page size<br>0.6 □ TRAM favors energy efficiency | nali  |  |  |

|                       | N6                                                        | 512           | 0.512                                                             | δ <sup>0.6</sup> favors energy efficiency                                                         | norr  |  |  |

|                       | N7                                                        | 512           | 0.256                                                             |                                                                                                   | of n  |  |  |

|                       | N8                                                        | 512           | 0.128                                                             |                                                                                                   | 0     |  |  |

|                       | N9                                                        | 512           | 0.064                                                             | <b>X</b> N1 N2 N3 N4 N5 N6 N7 N8 N9                                                               | A     |  |  |

|                       | Llaina Mamary Madala ta Evalara Maarithmia Chaica far Day |               |                                                                   |                                                                                                   |       |  |  |

#### Using Memory Models to Explore Algorithmic Choice for Power Provisioning

Power can be distributed to core or memory depending on the application's sensitivity to power changes on the given component. In this work we develop model's to capture an application's sensitivity to power changes in the memory by reducing the memory bus speed, which also reduces the per core memory bandwidth. Reducing power to memory system by reducing memory bus frequency.

- > Memory bus frequency also reduces per core memory bandwidth.

- Growth of multi-core means also means less per core memory bandwidth

- > Future systems will most likely continue to have reduced per core memory bandwidth

- Models identify sensitivities of algorithms to reduced per core memory bandwidth (e.g. reduced memory power)

- Models aid in algorithmic choice for future systems

**Determining the algorithm sensitivity to power changes using models** Models of 3 different algorithms for AMG application 🗕 - Parasai

📥 – Hybrid Parasails most sensitive eductions in B Note the models identify algorithmic choices that are less sensitive to power reductions in the main memory enabling optimal decisions in power budgeting for applications. Details in Tiwari-Cluster'14.

# SUPER Power Awareness for HPC

Laura Carrington (Lead), Ananta Tiwari Rob Fowler UCSD/PMaC RENCI

## **Power Monitoring with PAPI**

The latest PAPI release (a.k.a. MIC) architecture

e convenient for users only the application is

oplications running on ally instrumenting the

sAPI (distributed with

on the card (uW)

age (uV), Power reading (uW

**CASE STUDY** We measure power usage in Figure 1(a) and energy consumption in 1(b) of a Hessenberg reduction computed on the Xeon Phi coprocessor utilizing all 244 cores. nic0:tot0 ENERGY (kWs) -(a) Power Usag (b) Energy Consumptio

## level

## **Power & Performance Analysis**

the performance response to reductions in the memory frequency or power. Models are fine-grained and capture the different computational phases within an application and their different responses.

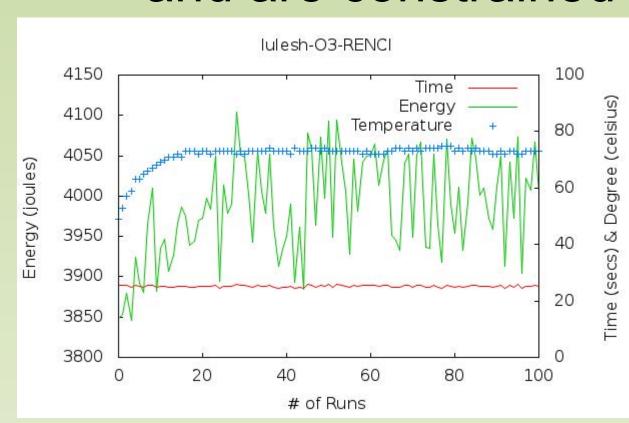

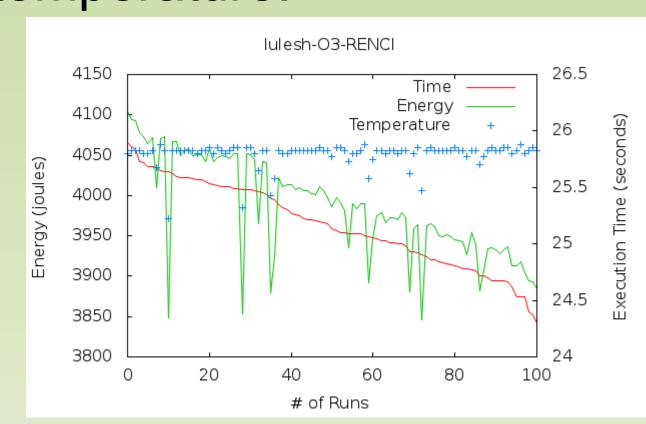

100 Lulesh runs sorted by execution order.

#### Processors are not identical:

- Two "identical" chips at the same clock speed will have different voltages and temperatures, or need to have different speeds for identical temperature bounds.

- Actual cooling capacity varies between sockets, blade slots, chassis, ...

- Performance heterogeneity induces effective load imbalances where none should exist.

- Imbalances look too "small" to fix by moving work around.

- Faster processors waste energy by racing ahead of synchronization partners.

### Recent processors use adaptive control to adjust performance within a temperature/power envelope.

- Hardware dynamically adjusts clock and voltage.

- Programmer accessible controls:

- Complete manual override of HW control.

- Per core clock cycle skipping (a.k.a. clock modulation)

- Set power capping policy used by HW control.

#### **Approach:** Apply Power Capping and Clock Modulation to smooth synchronization arrival times.

- Launch privileged daemon that accesses power MSRs using the batch system (Slurm).

- Monitor MPI\_wait () times to identify problems. • Use either power capping or modulation to adjust power and performance.

#### **Results:**

- Wasted energy is effectively scavenged.

- On a single chip, these methods have the potential of shifting the thermal budget to

- the cores that can benefit.

UTK

Heike McCraw Shirley Moore, Rogelio Long UTEP

#### **POWER MONITORING ON IBM BLUE GENE/Q**

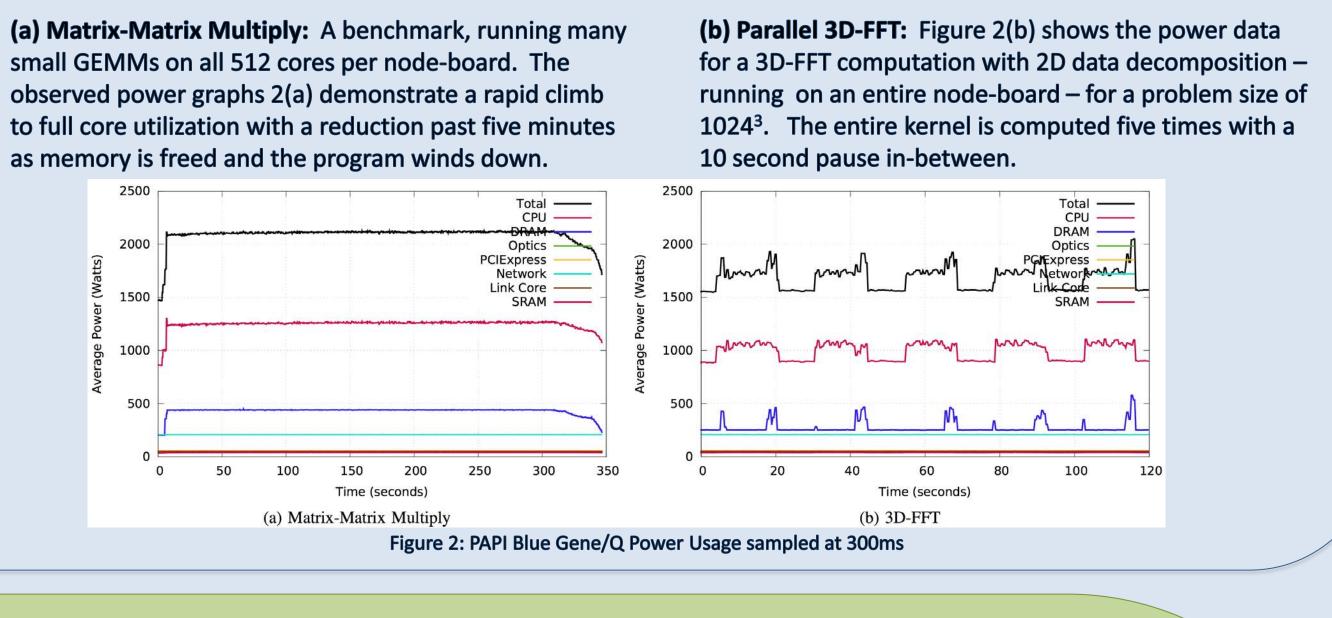

The PAPI "bgq-emon" component exposes power data through the IBM EMON API. Power is supplied to an entire node-board by two identical main power modules, each providing seven high voltage Direct Current (DC) power lines (a.k.a. "domains"). Each power domain from one main power module is paired with the equivalent domain from the other module, and a step-down transformer provides final voltage for the compute cards.

The domains – which are also the power statistics that can be monitored through the PAPI bgq-emon component -- are described in the following Table:

| Domains | Description                            |

|---------|----------------------------------------|

| 1       | Chip core voltage (0.9V)               |

| 2       | Chip memory interface and DRAM (1.35V) |

| 3       | Optics (2.5V)                          |

| 4       | Optics and PClexpress (3.5V)           |

| 6       | Chip HSS network transceiver (1.5V)    |

| 8       | Link chip core (1V)                    |

| 7       | Chip SRAM voltage (0.9+0.15V)          |

Current is measured on each of the 14 domains leaving the main power modules Voltage is measured after the final step-down transformation. A complete sample is taken in  $\sim$ 500µs (the IBM EMON interface accesses this data from the nodeboard, which includes a 1-10ms blocking delay for the caller)

## Adapting to Power and **Performance Variability**

**Problem:** Computation speed and energy efficiency vary with and are constrained by temperature.

100 Lulesh runs sorted by execution time.

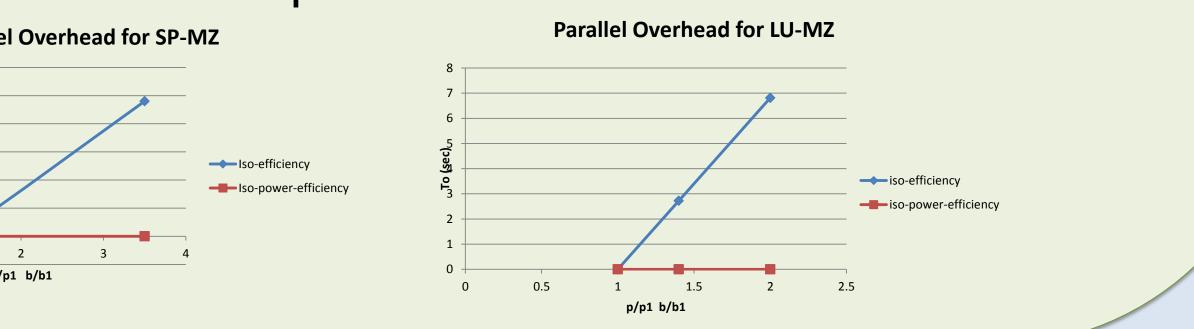

### **Iso-Power-Efficiency**

- cores.

$$T_o = \frac{p}{p_1} T_p$$

$$T_o = \frac{b}{b_1} T_b$$

- parallel efficiency E:

|           |    |   | Para |

|-----------|----|---|------|

|           | 6  |   |      |

|           | 5  |   |      |

|           | 4  | - |      |

| ec)       | 3  |   |      |

| I O (sec) | 2  |   |      |

|           | 1  |   |      |

|           | 0  |   |      |

|           | -1 | 0 | 1    |

|           | -  |   |      |

|           |    |   |      |

#### **CASE STUDIES**

On one rank per node-board we register to receive a standard SIGPROF Unix profiling signal, which, when received, triggers a routine to sample PAPI "bgq-emon" data. An ITIMER PROF system timer is then requested to trigger at an interval of 300ms, calling the sampling routine.

True cost of running an application is the energy used. Future machines will have a power bound and users will request a power budget when they submit a job.

Iso-efficiency behaves differently when scaling the problem size up with increasing power budget, rather than just the number of

where

$$p_1$$

is the minimum number of  $T_{p_1}$  processors that can be used

Iso-power-efficiency overhead function:

where b is the power budget and b1 is -T

$I_{b_1}$  the smallest power that can be used

The the Iso-(power)-efficiency function gives the rate at which we must scale up the problem size per core to maintain the same

$$W = \frac{E}{1 - E} T_o$$

Graphs below are using data from Patki et.al. ICS'13.  $T_0 = 0$  indicates we can achieve perfect linear strong scaling with fixed problem size or maintain constant efficiency with no increase in problem size per core:

el Overhead for SP-M